Digital Design Lab EEN 315

Lab 1 Title Lab/Project

Group 2 Andrew O'Neil-Smith (Partner: Austin Cliffton and Amy Zamon)

Sayan Maity, TA

University of Miami September 23, 2013

#### Abstract

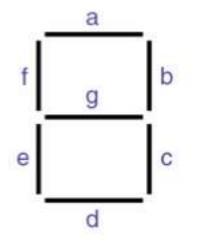

Part One was to design a 7-segment Display using only LED's and logic gates. In principle, a 7-segment display consists of 7 LED's arranged in the form of digit 8 as shown below. The LEDs are marked as (starting from the top and going clockwise) a, b, c, d, e, f, g.

Part two was to design a state machine that has a single input line X and a single output line Z.

The machine detects the input sequence 101 by producing Z=1 as the last 1 occurs, Z = 0 otherwise. Overlap is allowed.

Part three was to connect the two circuits so that when the output of the sequence detector is 1, 1 should show on the seven-segment display; otherwise, 0 should be displayed. Overlapping is okay. Should be completed with D Flip-Flops and NAND gates.

The key results were that we got a seven-segment display to properly display the numbers 0-9. We also got great results on the sequence detector.

The goal was to get familiar with the equipment we will be using this semester.

## **Table of Contents**

| 4  |

|----|

| 4  |

| 4  |

| 4  |

| 5  |

| 5  |

| 8  |

| 9  |

| 10 |

| 10 |

| 10 |

| -  |

#### Overview

The seven-segment display is a widely used logic circuit (ovens, clocks, etc). Each segment has a letter assigned to it (see figure). Each LED must be connected to ground and a signal through a resistor. The D Flip-Flop senses the sequence "101" and will display a "1" if detected. If not detected, a "0" will be displayed on the seven segment display. Understanding Boolean Logic and Algebra is key to knowing how to do this lab.

### **Objectives**

The objective was to build a seven-segment display using only NAND gates, as well as a sequence detector detecting the sequence "101."

### Equipment

| Description                          | Chip Number |  |  |  |  |

|--------------------------------------|-------------|--|--|--|--|

| Quad 2Input NAND gates               | 7400        |  |  |  |  |

| Triple 3 Input NAND gates            | 7410        |  |  |  |  |

| Quad 4 Input NAND gates              | 7420        |  |  |  |  |

| Dual Positive Edge-Triggered D<br>FF | 7474        |  |  |  |  |

### Description

Step one was to make a Truth Table for the seven-segment display. It has four X inputs and seven Letter outputs. The next step was to make K-Maps based on the Truth Table. We solved each K-Map and we realized the equations of Prime Implicants for the display. We then began to make each prime implicant on the breadboard with the NAND gates. Each integrated circuit had to be sent power and ground.

The sequence detector started with the State-Machine, followed by the next state table. We got the input requirements for detecting "101" from that. Then we used K-Maps to figure out the D Flip-Flop formulas. The clock was given manually via the buttons on the test bench.

### **Specifications**

Use only NAND gates for the 7 segment display. The sequence detector will use only NAND gates and one D Flip-Flop.

| Design Oynthesis |    |    |    |    |   |   |   |   |   |   |   |

|------------------|----|----|----|----|---|---|---|---|---|---|---|

| Truth Table      |    |    |    |    |   |   |   |   |   |   |   |

| Ν                | X1 | X2 | Х3 | X4 | Α | В | С | D | Ε | F | G |

| 0                | 0  | 0  | 0  | 0  | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1                | 0  | 0  | 0  | 1  | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 2                | 0  | 0  | 1  | 0  | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 3                | 0  | 0  | 1  | 1  | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 4                | 0  | 1  | 0  | 0  | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 5                | 0  | 1  | 0  | 1  | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 6                | 0  | 1  | 1  | 0  | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 7                | 0  | 1  | 1  | 1  | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 8                | 1  | 0  | 0  | 0  | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 9                | 1  | 0  | 0  | 1  | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 10               | 1  | 0  | 1  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 11               | 1  | 0  | 1  | 1  | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 12               | 1  | 1  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 13               | 1  | 1  | 0  | 1  | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 14               | 1  | 1  | 1  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 15               | 1  | 1  | 1  | 1  | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

### **Design Synthesis**

$PI_1 = \overline{X}_1 \times_3 \overline{X}_4 \qquad PI_6 = \overline{X}_1 \times_2 \overline{X}_4 \overline{26} PI_1 = \overline{X}_1 \overline{X}_3 \overline{X}_4$  $VPI_2 = \overline{X_1} \overline{X_2} \overline{X_3}$   $VPI_2 = \overline{X_2} \overline{X_3}$   $VPI_{12} = \overline{X_1} \overline{X_3} \overline{X_4} \overline{F44}$  $PI_{4} = \overline{X_{1}} \overline{X_{2}} \overline{X_{3}} PI_{8} = \overline{X_{1}} \overline{X_{2}} PI_{13} = \overline{X_{1}} \overline{X_{3}}$   $PI_{4} = \overline{X_{1}} \overline{X_{2}} \overline{X_{3}} U PI_{4} = \overline{X_{1}} \overline{X_{4}} PI_{4} = \overline{X_{1}} \overline{X_{2}} \overline{X_{3}} \overline{X_{4}}$ 1 PIS = X2X3 X4 JPIO = XX220 - PIIS = X1X2X4  $V = \overline{X_1} \times 3 + \overline{X_2} \times 3 \times 7 + \overline{X_1} \times 2 \times 3 + \overline{X_1} \times 2 \times 4$   $P_{T_13} \qquad P_{T_3} \qquad P_{T_$  $B = \overline{X_1} \overline{X_2} + \overline{X_2} \overline{X_3} + \overline{X_1} \overline{X_3} \overline{X_4} + \overline{X_1} \overline{X_3} \overline{X_4}$  $\int C = \overline{X}_2 \overline{Y}_3 + \overline{X}_1 \overline{X}_2 + \overline{X}_1 \overline{X}_2 + \overline{X}_1 \overline{X}_1 \overline{X}_2$   $= PT_2 - PT_2$  $\begin{array}{c} D = \overline{X_1 X_3 X_4} + \overline{X_1 X_2 X_3} + \overline{X_1 X_2 X_3} + \overline{X_2 X_3 X_4} + \overline{X_1 X_2 X_3 X_4} \\ PI_1 & PI_2 & P_3 & PI_5 & PI_4 \end{array}$ / E= X2 X3 X4 + X, X3 X4 PE5 PET P1  $\begin{array}{c|c} F = \chi_1 \overline{\chi_2} \overline{\chi_3} + \overline{\chi_1} \chi_2 \overline{\chi_3} + \overline{\chi_1} \overline{\chi_3} \overline{\chi_4} + \overline{\chi_1} \overline{\chi_2} \overline{\chi_4} \\ P \overline{\Gamma_3} & P \overline{\Gamma_4} & P \overline{\Gamma_{11}} & P \overline{\Gamma_{15}} \end{array}$  $VG = \overline{X}_{1} \times_{3} \overline{X}_{4} + \overline{X}_{1} \overline{X}_{2} \times_{3} + \overline{X}_{1} \overline{X}_{2} \overline{X}_{3} + \overline{X}_{1} \times_{2} \overline{X}_{3}$   $PI_{1} \qquad PI_{2} \qquad PI_{3} \qquad PI_{4}$ 1: DG 6:A II: BEF 2: DG 7: BC 12: B 3: ADFG 8: C 13: A 4: FG 9: C 14: D S: ADE 10: B 15: F

These are the Finne implicants and boolean Equations.

#### <u>K-Maps</u>

| x1x2<br>x3x4 | 1<br>0<br>1<br>1 | <b>A</b><br>0<br>1<br>1      | 0<br>0<br>0 | 1<br>1<br>0<br>0 |

|--------------|------------------|------------------------------|-------------|------------------|

| x1x2<br>x3x4 | 1<br>1<br>1<br>1 | <b>B</b><br>1<br>0<br>1      | 0<br>0<br>0 | 1<br>1<br>0<br>0 |

| x1x2<br>x3x4 | 1<br>1<br>1<br>0 | <b>C</b><br>1<br>1<br>1      | 0<br>0<br>0 | 1<br>1<br>0<br>0 |

| x1x2<br>x3x4 | 1<br>0<br>1<br>1 | <b>D</b><br>0<br>1<br>0      | 0<br>0<br>0 | 1<br>1<br>0<br>0 |

| x1x2<br>x3x4 | 1<br>0<br>0<br>1 | <b>E</b><br>0<br>0<br>1      | 0<br>0<br>0 | 1<br>0<br>0      |

| x1x2<br>x3x4 | 1<br>0<br>0      | <b>F</b><br>1<br>1<br>0<br>1 | 0<br>0<br>0 | 1<br>1<br>0<br>0 |

| x1x2<br>x3x4 | 0<br>0<br>1<br>1 | <b>G</b><br>1<br>1<br>0<br>1 | 0<br>0<br>0 | 1<br>1<br>0<br>0 |

Complete Logic Diagram

# **Results and Simulations**

1 through 9

### Answers to the questions in the lab handout

1.

**2.** One other use is the transmission of music control data in MIDI (Music Instrument Digital Interface). The sequence detector senses when note "on" and "off" events occur. It is constantly trying to read a stream of messages.

#### Conclusion

The project had us create a seven-segment display and a sequence detector using NAND gates. The hardest part of the design was finding time that we could all work on it. It was a challenge to all work equal amounts on it. Our final design could have been neater in terms of wire lengths. I have learned how to get a seven-segment display to work using only NAND gates. I have also learned how to implement a sequence detector.

### **Works Cited**

None